要点

- パワートランジスタ(Si-IGBT)のスケーリングよる性能向上を実証

- オン状態の抵抗を従来技術の約50%に低減

- 現在、市場で主流のSi-IGBTのさらなる高性能化・低価格化へ

概要

東京工業大学 科学技術創成研究院 未来産業技術研究所の筒井一生教授らは、シリコンによる電力制御用の絶縁ゲート形バイポーラトランジスタ(IGBT)[用語1]をスケーリング(微細化)することで、コレクタ-エミッタ間飽和電圧(Vce(sat))[用語2]を従来の約70%に、オン抵抗を約50%に低減することに成功した。

スケーリングには素子寸法の「3次元的微細化」という新スキームを用いた。性能向上はオン動作時の単位面積あたりの電流密度を高めることで実現した。現在、主流のシリコン(Si)-IGBTのスケーリングによる性能向上が確認でき、市場のさらなる拡大とともに、電力制御システムの高効率・低価格化につながる技術として、省エネルギー社会への貢献が期待される。

この研究は新エネルギー・産業技術総合開発機構(NEDO)による「新世代Si-IGBTと応用基本技術の研究開発」(代表:平本俊郎東京大学教授)で行われた。研究成果は12月6日に米サンフランシスコで開かれる国際会議International Electron Devices Meeting(IEDM2016)で、東工大、東大、九州工業大学、明治大学、産業技術総合研究所、東芝、三菱電機の共同研究として発表される。

研究成果

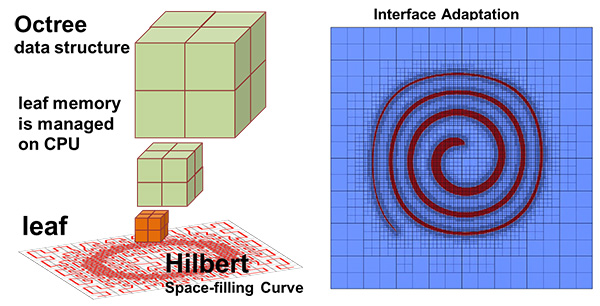

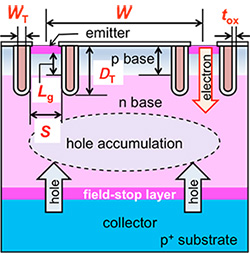

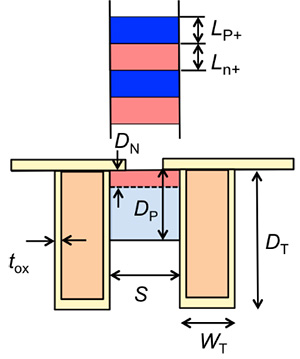

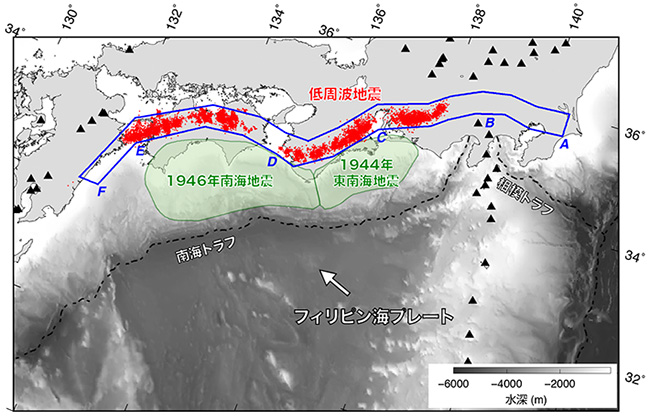

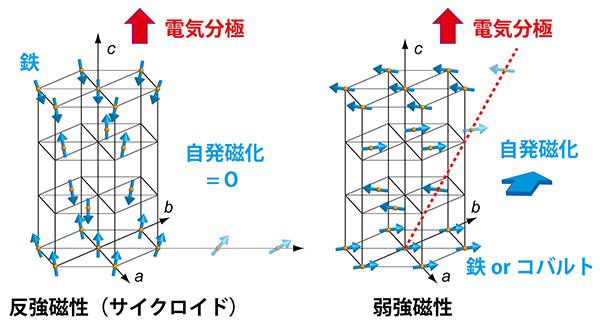

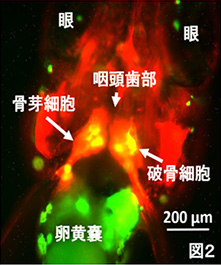

図1および図2に作製したSi-IGBTの断面と垂直方向の構造、各部の寸法変数を示す。図1の上部(表面)に間隔Sで接近形成した縦のトレンチ(溝)ゲートに挟まれたエミッタ領域から電子電流が流入し、それに応じた正孔電流が下部(裏面)全面のコレクタ領域から流入することで、全体に縦方向のオン状態の電流が流れる。一方、トレンチゲートに加えるゲート電圧の制御によってエミッタからの電子電流の流入を止めることにより正孔電流も止まり、全体がオフの電流遮断状態になる。このようなIGBTの構造と電流をオン・オフする動作は通常のデバイスと変わらない。

![Si-IGBTの断面構造]()

図1. Si-IGBTの断面構造

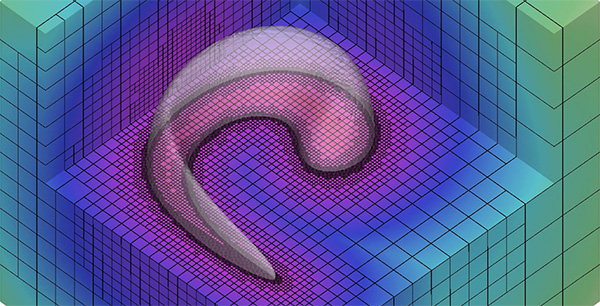

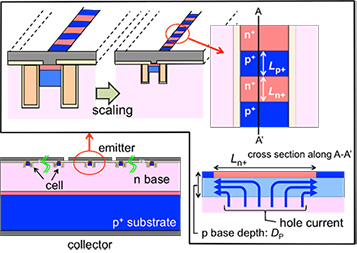

![Si-IGBTの断面および奥行き方向の構造]()

図2. Si-IGBTの断面および奥行き方向の構造。ラッチアップ現象を抑制するため、奥行き方向のp領域とn領域の繰り返し寸法もスケーリングの対象となっている。

現在、製品化されているIGBTと同様の寸法のデバイスと、新規のスケーリングの概念により微細化した新構造デバイスを製作し、特性を比較した。図3と表1に両デバイスの寸法の比較を示す。寸法の微細化の比率をスケーリングファクタ1/kで表し、従来デバイスがk=1、新デバイスがk=3に対応する。

![IGBTの3次元方向にわたる各構造寸法の変数]()

図3. IGBTの3次元方向にわたる各構造寸法の変数。表1の各項目に対応

表1. スケーリングによる各部の寸法およびゲート電圧(Vg)とスケーリングファクタ

Parameters in IGBT, symbol |

k=1 |

k=3 |

Scaling factor |

Cell pitch, W (µm) |

16 |

16 |

1 |

Mesa width, S (µm) |

3 |

1 |

1/k |

Trench depth, DT (µm) |

6 |

2 |

1/k |

Trench depth, WT (µm) |

1.5 |

1.0 |

2/k |

p-base depth, DP (µm) |

3 |

1 |

1/k |

n-emitter depth, DN (µm) |

0.4 |

0.13 |

1/k |

Gate oxide thickness, tox (µm) |

100 |

33 |

1/k |

Length of p* region, Lp+ (µm) |

4.5 |

1.5 |

1/k |

Length of n* region, Ln+ (µm) |

4.5 |

1.5 |

1/k |

Gate voltage, Vg (V) |

3 |

1 |

1/k |

断面構造で、トレンチゲート周りの寸法は1/kに比例縮小する一方で、隣接するトレンチゲートまでの距離(W)(図1参照)は一定とした。IGBTの2次元のスケーリングは相補型金属酸化膜半導体(CMOS)のスケーリングと違って縦横のスケーリングが及ぼす効果が逆に働くこともあり、その効果は複雑だが、すでにシミュレーションでは単位面積あたりのオン電流の密度を増大することが予測されていた。その予測を今回、デバイスを試作して初めて実証した。

さらに試作に当たってスケーリングパラメータを一部見直すとともに、デバイスの奥行き方向に交互に作られる表面のp形領域とn形領域のピッチ(Lp+およびLn+)も1/kに縮小した。これはスケーリングで予測されるラッチアップ耐性[用語3]の劣化に対する対策である。この奥行き方向のスケーリングを含めて3次元スケーリングと呼んでいる。

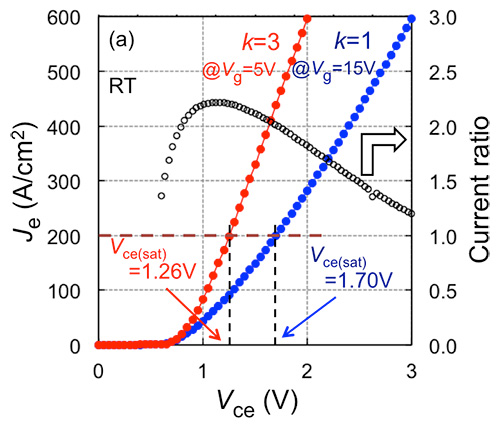

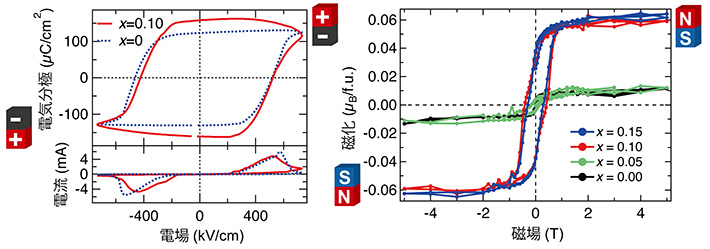

図4に試作したSi-IGBTのオン状態でのコレクタ-エミッタ間の電流-電圧特性を示す。同じオン電流密度(飽和電流密度:Ice(sat)、図では200 A/cm2)における電圧をエミッタ-コレクタ間飽和電圧(Vce(sat))と呼ぶが、これがk=3のスケーリングで、従来(k=1)に比べ約70%の1.26 Vが得られた。また、同じエミッタ-コレクタ間電圧(Vce)における両デバイスの電流比も同図に示し、スケーリングにより電流が約2倍、すなわちオン抵抗が半減したことがわかる。これらはいずれも、IGBTのオン動作においてデバイス内部でのエネルギー損失に比例するため、スケーリングによりIGBTの低損失・高効率化が実現できたことを示している。

- 図4.

- 試作した2つのIGBTのオン状態におけるエミッタ-コレクタ間電流-電圧特性。特定の電流密度(図では200 A/cm2)における電圧がエミッタ-コレクタ間飽和電圧(Vce(sat))と定義される。Vce(sat)がスケーリング(k=1→k=3)により1.70 Vから1.26 Vに低減(約70%)している。また、一定電圧における電流がk=3で倍増しており、オン抵抗が半減したことを示す。

一方、ゲート電圧(Vg)も、スケーリングにより低い電圧(k=3において5 V)で動作している。

また、表1および図4に示すように、寸法とともにIGBTの制御入力の電圧となるゲート電圧(Vg)も従来の15 Vから5 Vに低下させた。これにより、将来、IGBTを駆動するゲートドライブ回路の消費電力が大幅に低減されるとともに、従来のSi-CMOS回路技術との親和性が高まる。このことは、回路、システムレベルでの高性能化と低コスト化につながることが期待される。

なお、このスケーリングはIGBTのゲート周りの微細化であり、トランジスタの耐圧を決めるその下のn-ベース層の厚さは変えないので、n-ベース層の厚さの選択によって従来のIGBTが持つ1000~数1000Vの耐圧はそのまま維持される。

表2に、今回の新構造IGBT(k=3)を現在市場にある製品も含めて比較したベンチマークを示す。VgおよびVce(sat)(常温と150 - 175 ℃で)の低減が達成された。

表2. 今回試作したIGBT(k=3およびk=1)と市場に出ている製品の例で特性を比較したベンチマーク

|

This work

k=3 |

This work

k=1 |

IGC99T120

T8RM |

FGW25N

120W |

Blocking voltage (V) |

1200 |

1200 |

1200 |

1200 |

Vg (V) |

5 |

15 |

15 |

15 |

Vce(sat) Tj=25 ℃ |

1.26 |

1.70 |

1.75 |

2.0 |

Vce(sat) Tj=150 - 175 ℃ |

1.26 |

1.95 |

2.05 |

2.6 |

背景

省エネルギー化には電力制御システムの高効率化が重要である。そのシステムは大規模では発電、送電、また鉄道や自動車から、小さいものでは家電製品やモバイル機器に組み込まれた電源回路に至るが、そこにはインバータに代表される電力制御装置が必須で、それを構成するパワー半導体トランジスタがその性能と製造コストに大きな影響を与える。

パワートランジスタの市場は価格の面からSi-IGBTが主流で、今後10年以上にわたってこれは揺るがないと予想されている。Si-IGBTは種々の技術革新により高性能化、小型化と低コスト化を進めてきたが、昨今はその進化が飽和する傾向となり、デバイス技術のコモディティ化も予想され、次世代に向けた新たな技術革新が求められている。

これまで日本はパワー半導体トランジスタの分野では世界の中で優位にあった。この分野での日本の産業力を今後も維持するためにも、日本発の新技術開発は大きな意義があり、特にその主流であるSi-IGBTの性能への技術革新は極めてインパクトが大きい。

Si-IGBTの性能面では、低損失化が重要で、そのためにはオン抵抗の低減が必要である。新しい方法としてスケーリングに注目して、これを実現したのが今回の研究成果である。

研究の経緯

Si-IGBTのスケーリングによる高性能化技術は、2012年に九州工業大学の大村一郎教授らにより理論モデルをベースに提案された。これは、IGBTの電流制御を行うトレンチゲート周りの構造を幅方向と深さ方向に2次元的に縮小し、かつ、隣接するトレンチゲート構造同士の距離は広く保つという2次元的なスケーリングを行うものであり、特許提案を行っている。大村教授らは今回の研究を推進しているNEDOプロジェクトでの共同研究グループの一つである。

スケーリング技術はデバイスシミュレーションに基づく提案だったが、実デバイスでの実証はこれまでなかった。実デバイスの作製には、構造設計において2次元の単純スケーリングスキームを試作に適したものに焼き直して、その特性を予想することや、プロセス技術の探索が要求され、さらにラッチアップ耐性の対応策の検討も必要である。

また、トランジスタ単体の技術にとどまらず、これを使う回路技術上の課題もあった。このように基礎から応用まで含めた幅広い研究の必要性から現在の日本の産業界だけでこの研究を推進していくことは困難が伴い、産官学の連携が強く望まれていた。

この課題を解決するため、2014年に産官学のNEDOプロジェクトが始まり、スケーリングによる新構造IGBTの試作研究とそれを活かす回路技術研究を密接に結びつけた体制のもとで研究が推進され、デバイス技術側での重要なマイルストーンとなる今回の研究成果を得た。

今後の展開

Si-IGBTは価格の面から少なくとも今後10年はパワーデバイスの主流を占めると予想されているが、一方で、性能向上の限界に近付いているともいわれてきた。今回の成果によって、スケーリングによる性能の向上が確認されたことは、日本がこれからもSi-IGBTという主流市場で価格競争でなく性能による差別化で勝負できるという意味で重要である。

また今回の実証は1/3のスケーリングであるが、さらにそれ以上の可能性も秘めた技術である。Si-IGBTのエネルギー損失を顕著に低減するこの技術が産業レベルで実用化されれば、電力制御システムの高効率化に直接貢献できる。またドライブ回側での技術開発により低電圧駆動が実用化されれば、システムとしてさらに高効率化、高機能化と低コスト化が実現し、これが世界に広く普及すれば将来の省エネルギー社会の実現への貢献が期待できる。

用語説明

[用語1] 絶縁ゲート形バイポーラトランジスタ(insulated gate bipolar transistor: IGBT) : エミッタ電極とコレクタ電極の間の電流を、絶縁層を介したゲート電極に加える制御電圧信号により制御するトランジスタ。高電圧、大電流を直接オン・オフできる高性能パワートランジスタとして広く用いられている。

[用語2] コレクタ-エミッタ間飽和電圧(Vce(sat)) : トランジスタがオン状態になるゲート電圧を入力している状態で、ある一定のエミッタ-コレクタ間電流密度におけるエミッタ-コレクタ間の電圧。この電圧と電流の積がトランジスタ内部でのエネルギー損失になるため、電圧を低減することが高効率化に重要である。

[用語3] ラッチアップ耐性 : 薄い導電層に電流を横方向に流すことによりその層の電位が変動し、本来は絶縁状態にあるp形層とn形層の積層構造中に過剰電流が流れ、デバイス中に制御できない過剰電流がながれてしまう現象がラッチアップ。十分なラッチアップ耐性の確保はパワーデバイスにとって重要である。

参考資料

International Electron Devices Meeting(IEDM2016)で出版されるTechnical Digest(会議録)に掲載される論文:

K. Kakushima, T. Hoshii, K. Tsutsui, A. Nakajima, S. Nishizawa, H. Wakabayashi, I. Muneta, K. Sato, T. Matsudai, W. Saito, T. Saraya, K. Itou, M. Fukui, S. Suzuki, M. Kobayashi, T. Takakura, T. Hiramoto, A. Ogura, Y. Numasawa, I. Omura, H. Ohashi, and H. Iwai;

"Experimental Verification of a 3D Scaling Principle for Low Vce(sat) IGBT";

Technical Digest of IEDM2016, 講演番号:10.6, (2016).