要点

- 3次元積層デバイスの熱抵抗[注1]計算法を確立

- バンプとTSVを組み合わせた垂直配線に比べ、バンプレスTSVの熱抵抗は1/3に

- IoT時代に欠かせない大容量メモリーの多層積層を3倍に

概要

東京工業大学 科学技術創成研究院 未来産業技術研究所の大場隆之教授はWOWアライアンス[用語1]と共同で、バンプレスTSV配線[用語2]を用いると、3次元積層デバイスの熱抵抗を従来のバンプ[用語3]の接合構造と比較して、30数%(1/3)まで低減できることを明らかにした。有限要素法(FEM)[用語4]と熱回路網の計算手法を用いて解析した。

解析により、バンプ接合TSV配線の3次元積層デバイスは積層部、絶縁層、有機膜が熱抵抗の主要因であることがわかった。これに対し、バンプレスTSV配線は、バンプの密度を同じにした場合、接合部の熱伝導が150倍良好であり、全体の熱抵抗では、従来手法が1.54 Kcm2/Wであるのに対して、0.46 Kcm2/Wにまで低減可能であることがわかった。

この成果は山形県天童市で4月19~21日に開かれるエレクトロニクス実装国際会議「ICEP2017」で発表された。

背景

3次元積層デバイスは、上下の接続層において、アンダーフィル材料[用語5]のような、絶縁膜、有機膜を使用する必要があるために、熱抵抗が大きくなり、放熱技術が非常に大きな課題となっている。そのため、大場教授らはウエハーを薄化してから積層し、TSVで直接上下チップを接続配線するバンプレスTSV配線を開発した。この技術を用いると、積層方向の熱抵抗の低減が期待できる。実際に従来の積層手法と比較して、バンプレスTSV配線の熱抵抗がどの程度低減するのかを推定した。

研究成果

大場教授らの研究グループは、ウエハーを薄化してから積層し、TSVで直接上下チップを接続配線するバンプレスTSV配線を開発している。この方法を用いれば、バンプが不要になり、薄化プロセスの限界までウエハーを薄くすることができる。また、この方式においては、各層間の接続に、TSV配線を利用できるために、接続部の熱抵抗が低減できると期待される。

今回、全体の熱抵抗を見積もるために、(1)3次元積層デバイスの構造を仮定する、(2)「各層の熱抵抗はFEMを用いて推定する、(3)全体の熱抵抗を熱回路網解析で推定する、という手順で実施した。

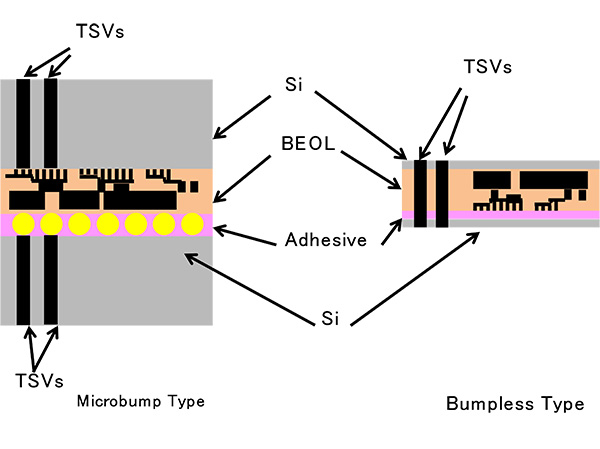

3次元積層デバイスはマイクロバンプタイプとバンプレスタイプの断面構造の比較図(図1)に示したように、シリコン基板、TSV設置シリコン基板、BEOL[用語6]、垂直方向の接合構造(マイクロバンプ構造、バンプレス構造)で構成されている。今回の研究では、BEOLと垂直方向の接合構造の熱抵抗に関しては、FEMで熱伝導率を推定、また、全体の熱抵抗の計算に関しては、熱回路網を用いて推定した。

図1. マイクロバンプタイプとバンプレスタイプの断面構造の比較図

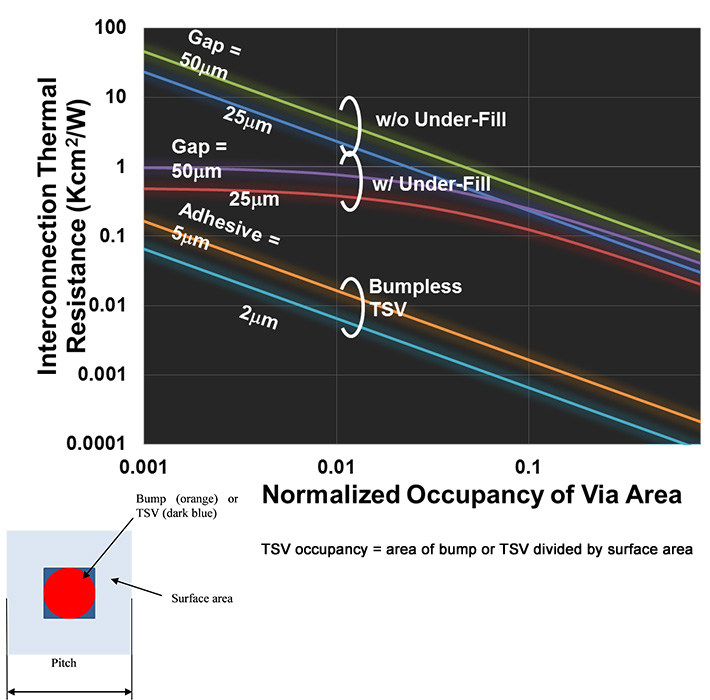

総合的な熱抵抗の推定において、マイクロバンプ構造の熱抵抗の計算に関しては、参考文献[1]の計算手法を参考に計算した。このとき、直径25マイクロメートル(μm)のマイクロバンプを使用し、50 μmピッチで配置した際の、全体の熱抵抗は1.54 Kcm2/Wと算出することができ、熱抵抗が高い要因の多くが、BEOLと垂直配線の接合構造にあることがわかった。

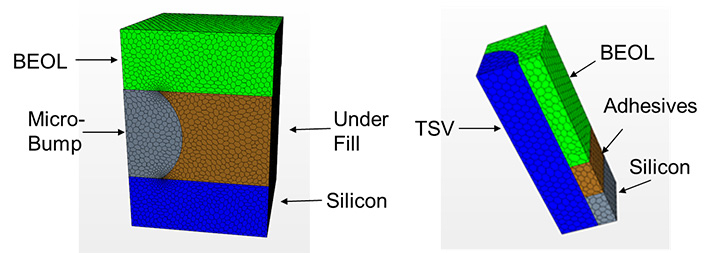

次に、各要素のFEM解析を図2に示すようなモデルを用いて等価熱伝導率を推定していくことにより、バンプレスタイプの熱抵抗を推定した。その結果を図3に示す。同じバンプレスタイプの垂直方向の接合の熱抵抗は、マイクロバンプタイプのそれと比較して、同じ占有率を想定した場合、150倍小さくなることが推定できた。

図2. マイクロバンプタイプとバンプレスタイプのFEMモデルの比較

図3. 垂直接合部の熱抵抗の占有面積依存性のグラフ

この結果から、バンプレスのTSVの密度を全体の1%程度にまで減らしたとしても、熱抵抗が改善できることが分かる。そのため、TSVの本数としては、信号線として使用される本数を想定することで、放熱性としては、十分であることが分かった。

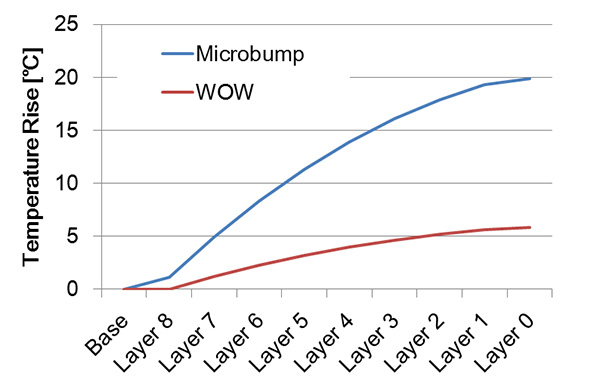

この各要素の熱抵抗から、全体の熱抵抗を計算したところ、従来のマイクロバンプの方式では、1.54 Kcm2/Wであるのに対して、0.46 Kcm2/Wにまで低減可能であることがわかった。また、各要素の熱抵抗と各層の発熱量から、それぞれの温度上昇を推定したところ、マイクロバンプタイプでは約20 ℃の温度上昇が推定されるのに対して、バンプレスタイプは、約4 ℃の温度上昇ですむことが推定された。

図4. マイクロバンプタイプとバンプレスタイプの温度上昇の比較グラフ

以上の結果から、現行の温度上昇を許容するとした場合、3~4倍のDRAM積層が可能になる。仮に、現在量産されている積層DRAMが2 GBであれば、6~8 GBに容量を増やすことができる。このようなメモリーの大容量化はIoT(モノのインターネット)に向けた応用が期待される。

今後の展開

薄化ウエハーの積層と高密度TSV配線で実証実験を行い、携帯端末およびサーバー向け大容量メモリー技術として実用化を行う。

[注1] 熱抵抗 : 熱の伝わりにくさを表す値のこと。半導体は高発熱体であるため、熱が伝わりにくくなると、半導体の温度が上昇し、動作不良の原因になる。最新の半導体では、単位面積当たり100 Wから300 Wの発熱が起きる。

用語説明

[用語1] WOWアライアンス : 東京工業大学を中心に設計・プロセス・装置・材料半導体関連の複数企業および研究機関からなる研究グループ。薄化したウエハーを簡単に積層することができ、バンプレスTSV配線を用いた三次元化技術に世界で初めて開発に成功した。

[用語2] TSV配線 : Through-Silicon-Viaの略で、シリコンウエハーを貫通させ埋め込み配線で上下チップチップを接続させる接続孔。最近では、シリコン材料以外にも配線するため、前工程における垂直配線(vertical interconnects)とした方がわかりやすい。

[用語3] バンプ : 電極部にメッキで形成した配線接続のための突起。

[用語4] FEM : Finite Element Method の略。有限要素法という数値解析手法の一種。

[用語5] アンダーフィル材料 : バンプが形成されたICチップを実装される際に用いられる絶縁材料。

[用語6] BEOL : Back End of Line の略。半導体前工程の中の金属配線層作成プロセス、および、このプロセスで作成された層のことを指す。

参考文献

[1] Matsumoto, et al., "Thermal Design Guidelines for a Three-dimensional (3D) Chip Stack, Including Cooling Solutions", 29th IEEE SEMI-THERM Symposium, 2013

論文情報

掲載誌 : |

IEEE 2017 International Conference on Electronics Packaging (ICEP), pp. 822-825 (2017) |

論文タイトル : |

A Design Guide of Thermal Resistance down to 30% for 3D Multi-stack Devices |

著者 : |

H. Ryoson, K. Fujimoto, and T. Ohba |

お問い合わせ先

東京工業大学 科学技術創成研究院

未来産業技術研究所 異種機能集積研究コア

秘書 沼沢文恵

E-mail : numazawa.f.aa@m.titech.ac.jp

Tel : 045-924-5866

取材申し込み先

東京工業大学 広報・社会連携本部 広報・地域連携部門

E-mail : media@jim.titech.ac.jp

Tel : 03-5734-2975 / Fax : 03-5734-3661