要点

- マイクロプロセッサおよびシステムオンチップ(SoC)におけるコアの待機時電力の削減に有効な不揮発性SRAM[用語1]を用いた新たな低消費電力技術(パワーゲーティング)を開発した。

- 不揮発性メモリ素子(強磁性トンネル接合;MTJ[用語2])をSRAMに組み込んだ不揮発性SRAMの設計法および駆動法を開発してチップ試作を行った。

- 試作チップの評価結果から、不揮発性SRAMを用いたパワーゲーティングのエネルギー性能を解析して、この技術を用いれば、マイクロプロセッサおよびSoCの課題となっていたコア部(演算を行うプロセッサの中心部分)におけるパワーゲーティングのエネルギー削減効率を大幅に向上できることを明らかにした。

概要

東京工業大学 科学技術創成研究院 未来産業技術研究所の菅原聡准教授らの研究グループは、マイクロプロセッサやシステムオンチップ(SoC)のコア(演算を行うプロセッサの中心部分)における待機時電力を削減するために用いられているパワーゲーティングに不揮発記憶を導入することで、そのエネルギー削減効率を従来技術に比べて飛躍的に向上できる技術を開発した。

同グループが提案した不揮発性パワーゲーティング(NVPG)[用語3]は、電源を遮断しても記憶内容を保持できる不揮発記憶を利用して、ロジックシステムの電源遮断を頻繁に行い高効率に待機時電力を削減する方法である。マイクロプロセッサやSoC内のコアに含まれるレジスタやキャッシュなどの記憶回路を独自開発の不揮発性双安定回路[用語1]で構成して、通常動作をほとんど劣化させることなく、高効率にNVPGによるエネルギーの削減ができる。

今回、同グループが提案している不揮発性SRAM(NV-SRAM)の設計法・駆動法を開発し、チップ試作を行い、その実測結果の系統的な解析によって、NVPGがマイクロプロセッサやSoCにおけるコアの待機時電力の削減に極めて有効であることを明らかにした。これまでにも不揮発記憶を用いたマイクロプロセッサやSoCのパワーゲーティングに関する技術開発はあったが、コア外の低階層キャッシュなどへの適応に限られていた。今回の研究は、開発したNVPG技術がコアに含まれる高階層キャッシュに搭載することが可能で、コアレベルのパワーゲーティングによる待機時電力削減効率を飛躍的に向上できることを明らかにした。

今回の研究成果は、9月12日からスイス・ローザンヌで開催された欧州最大の半導体技術に関する国際会議ESSDERC/ESSCIRCで発表された。

背景と研究の経緯

近年のパーソナルコンピュータやサーバに搭載されているマイクロプロセッサや、スマートフォンなどのモバイル機器に搭載されているシステム・オン・チップ(SoC)では、トランジスタのリーク(漏れ)電流によって待機時に消費する待機時電力が著しく大きく、その削減が重要な課題となっている。もし何も対策を講じなければ、この待機時電力は演算処理を行っているときの電力(ダイナミック電力)と同レベルとなり、無駄な電力を消費し続けてしまうことになる。このような待機時電力の削減に有効な技術にパワーゲーティングがある。待機状態にある回路ブロックへの電源供給を遮断することでリーク電流を削減するもので、マイクロプロセッサやSoCでは、コア部の電源遮断を行うコアレベルパワーゲーティングなどが広く用いられている。この技術では、電源遮断によってコア内のレジスタやキャッシュと呼ばれる記憶回路に保存されている重要なデータが失われるといった問題があるために、このデータを一度コア外のバックアップメモリに転送・保存してから電源遮断を行う。また、電源復帰時には、このデータをその都度コア内に書き戻す必要がある。パワーゲーティングでは、電源遮断を頻繁に行い(時間的細粒度という)、エネルギーの削減効率を高めることが重要であるが、この技術では、データの転送・バックアップ・書き戻しに必要な時間とこれに要するエネルギー消費が大きく、時間的細粒度のパワーゲーティングを実現できていない。すなわち、現状では効果はあるもののその本来の能力を十分に発揮できないという課題があった。

研究成果

同グループが提案した不揮発性パワーゲーティング(NVPG)は、不揮発記憶を利用して、ロジックシステムの電源遮断を頻繁(細粒度)に行い高効率に待機時電力を削減する方法である。コア内のレジスタやキャッシュなどを構成する各種CMOS双安定回路に不揮発性メモリ素子を組み込むことで、電源遮断を行ってもデータを保持できるところに特長がある。同研究グループの提案した不揮発性双安定回路では、CMOSロジックが通常の動作中には、不揮発記憶は用いずに通常の双安定記憶回路として動作し、電源遮断のときにだけ不揮発記憶を行うことができる。これによって、コア内の通常の高速動作には影響を与えず、高効率にエネルギーを削減できるNVPGが実行できる。

今回、同グループは提案している不揮発性SRAM(NV-SRAM)を試作し、その実測結果からNV-SRAMを用いてNVPGを実行した場合のエネルギー性能を系統的に解析した。この結果から、NV-SARMによるNVPGを用いれば、マイクロプロセッサおよびSoCの課題となっていたコア部におけるパワーゲーティングのエネルギー削減効率を大幅に向上できることを明らかにした。

研究成果の詳細

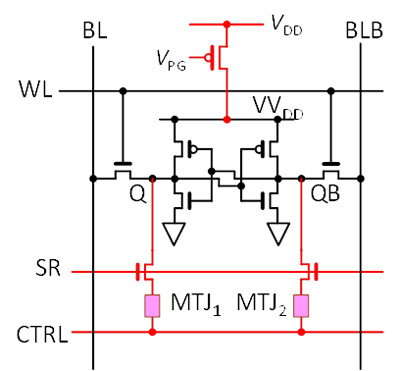

図1に同グループが提案しているNV-SRAMのセル構造を示す。通常のSRAMセルにトランジスタを介して、不揮発性メモリ素子である強磁性トンネル接合(MTJ)を接続してある。このトランジスタによって、通常動作時にはMTJをSRAMから電気的に切り離すことが可能となる。また、NV-SRAMに接続されたパワースイッチでセルへの電源遮断を行う。このセルを用いて、メモリアレイおよび周辺回路を構成してNV-SRAMの試作を行った。MTJの書き込み電流、各動作モードにおけるノイズマージンからセルの設計法を開発した。また、このセルでは通常の6トランジスタのSRAMセルと比べてトランジスタ数が増加しているが、セルへのバイアスを工夫することで、通常の6トランジスタSRAMセルと同じレベルのリーク電流に抑止できる駆動方法も開発した。また、MTJへの不揮発記憶の書き込みアーキテクチャや、動作電源遮断時のパワースイッチの駆動にも工夫を行い、セルアレイの各動作モードにおけるリーク電流を可能な限り削減した。

Clik here to view.

- 図1.

- NV-SRAMセルの回路構成。通常の6トランジスタSRAMセルの記憶ノードにトランジスタを介してMTJを接続してある。パワースイッチによって電源遮断を行う。

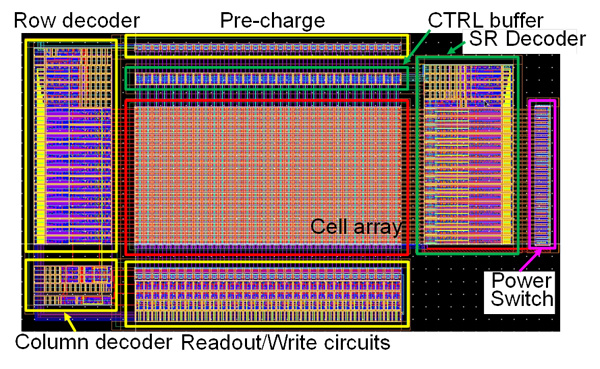

試作したNV-SRAMの設計レイアウトを図2に示す。通常のSRAMと同様の周辺回路に、不揮発記憶を行うための周辺回路を追加してある(後で述べるように、この不揮発記憶を行うための周辺回路はNV-SRAMのエネルギー性能に重要な影響を及ぼす)。CMOSのプロセス技術には65 nmのSOTB技術を用いた。この技術では、CMOS基板にバイアスを加えることで電源遮断時におけるトランジスタのリーク電流を大幅に削減することができる。この技術はセルアレイを駆動する周辺回路に採用した。

Clik here to view.

- 図2.

- 試作した NV-SRAMのレイアウト。基本構成は通常のSRAMと同じであるが、不揮発記憶のための周辺回路とパワースイッチを追加してある。

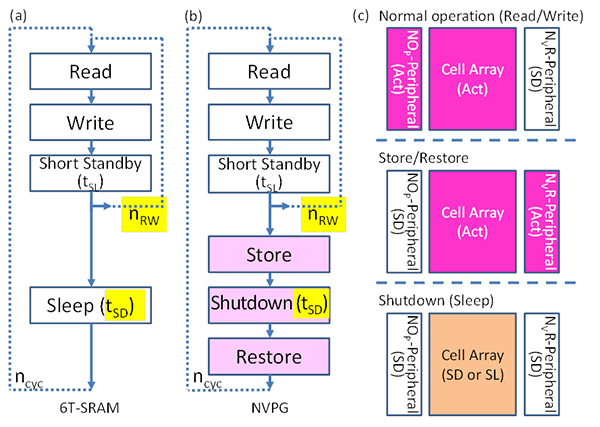

図3に評価に用いたベンチマークのシーケンスと各回路ブロックの動作モードを示す。通常のSRAM動作における読み出しと書き込みを全セルに対して、nRW回繰り返し、その後、電源遮断を行うときにだけ、MTJへの書き込みを行う。電源遮断を行わない短い時間の待機時はスリープモードとした(双安定回路のデータが消えない程度に供給電圧を絞る動作)。比較のための通常のSRAMでは、待機時はすべてスリープモードを用いた。周辺回路は各動作モードに合わせて、通電状態または電源遮断状態とした。作製したNV-SRAMの各回路部の各動作モードにおける電流値の実測値を用いて、パワーゲーティングの性能指標であるBreak-even time(BET)[用語4]からNV-SRAMのエネルギー性能を解析した。BETは電源遮断によってエネルギーを削減できる最低の電源遮断時間である。

Clik here to view.

- 図3.

- ベンチマークシーケンスと各回路ブロックの動作モード。NVPGではセルアレイの全ビットを読み出し/書き込み後、時間tSLのスリープモードを実行する。これをnRW回繰り返し、MTJに書き込み(ストア)してから時間tSDシャットダウンし、復帰(リストア)する。通常のSRAMでは、待機時はすべてスリープモードである。通常動作用と不揮発記憶用(NV-SRAMのみ)の周辺回路は使用しないときは電源遮断とする。

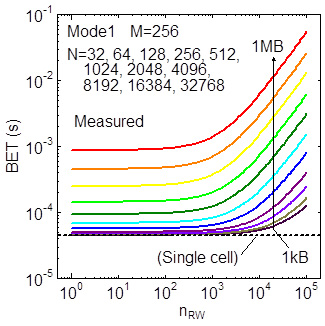

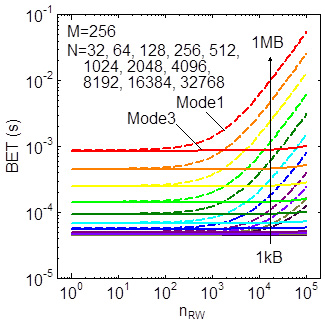

図4にBETのnRW依存性を示す。BETはnRWとアレイサイズ(Mビット×Nライン)によって変化する。nRWに依存せず一定の値をとるBETの領域では、BETは不揮発記憶時に消費するエネルギーによって決まり、アレイサイズが大きいほどBETは増大する。一方,nRWに依存して増大する領域では、BETは不揮発記憶用周辺回路のリーク電流に強く依存し、アレイサイズとともに増大する。なお、このようにBETがほぼ不揮発記憶のためのエネルギーと不揮発記憶用周辺回路のリーク電流で決まるのは、先に述べたように、セルのリーク電流を通常の6トランジスタSRAMセルと同程度まで減らしているために実現できる。

Clik here to view.

- 図4.

- Break-even time(BET)のnRW依存性。BETのnRWに対する挙動は、nRWとともに増大する領域と、nRWに依存せずに一定値をとる領域とに分けられる。それぞれ。図5、6の方法で削減できる。

nRWに依存して増大するBETは、不揮発記憶用周辺回路のリーク電流を削減することでその増大を抑えることができる。今回はSOTBの基板バイアスを用いて、削減を試みた。図5に結果を示す。この場合では、nRWに依存したBETの増加は大幅に抑制できた。

Clik here to view.

- 図5.

- SOTBの基板バイアスによって周辺回路のリーク電流を削減した場合におけるBETのnRW依存性(実線)。この場合では、nRWの広い範囲にわたって、BETはnRWに依存せず、一定値をとる。点線は図4の結果である。

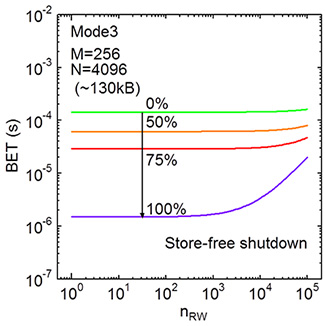

Nに依存して増大するBETは、ストアフリーシャットダウンと呼ばれるアーキテクチャを導入することで、削減できる。ストアフリーシャットダウンは既にMTJに書き込まれている内容がこれから書き込もうとする内容と一致するとき、または、セルの内容がMTJの内容と一致している状況から書き換わっていないときに、MTJへの不揮発記憶をスキップして電源遮断する方式である。結果を図6に示す。ストアフリーシャットダウンの比率が大きくなるとともにBETは削減できていることがわかる。

Clik here to view.

- 図6.

- ストアフリーシャットダウンの効果。MTJに記憶されている内容がSRAM部に記憶されている内容と一致するとき、MTJへの書き込みをスキップして、電源遮断する。ストアフリーシャットダウンの比率とともにBETを削減できる。

BETの値は、コア内のキャッシュに用いられるアレイサイズでは0.1 ms程度となり、ストアフリーシャットダウンの導入を考えるとさらに短いBETも期待できる。今回得られた結果は、従来に比べて桁で短い時間的粒度でコアレベルのパワーゲーティングが実現できる可能性を示している。

また、今回のNV-SRAM技術は、各階層のキャッシュのみならずレジスタファイルや、フリップフロップの不揮発化など、コア内の他の重要な記憶回路にも同様に拡張できる。これまでにも不揮発記憶を用いたマイクロプロセッサ/SoCのパワーゲーティングに関する技術開発はあったが、低階層のキャッシュなどへの適応に限られコアへの応用が困難であった。一方、本研究グループの開発したNVPG技術はコアレベルのパワーゲーティングに適し、従来技術以上に待機時電力削減効率を高めることが可能となる。

今後の展開

現在のマイクロプロセッサの高性能化ではマルチコア化が必須の技術になっているが、今後はさらに大規模なマルチコア化(メニーコア化)が重要になってくる。この一方でダークシリコンと呼ばれる各コアの消費エネルギーのため同時に動作できるコアの数に制限が加わるという問題も発生する。このような問題では各コアの低消費電力化がより重要となるが、NVPGはこのようなメニーコアのプロセッサに極めて有効な待機時電力削減アーキテクチャとなる可能性がある。

用語説明

[用語1] 不揮発性双安定記憶回路(不揮発性SRAM(NV-SRAM)、不揮発性フリップフロップ(NV-FF)) : NV-SRAMやNV-FFなどの不揮発性双安定回路はインバータループに不揮発性メモリ素子を直接接続することで実現できることは知られていたが、このような方式ではインバータループに接続された不揮発性メモリ素子が、通常の双安定回路の動作に悪影響を与え、動作速度の劣化や消費電力の増大、さらにはバラツキ耐性やノイズマージンの減少など回路性能の劣化を生じる。このため、通常動作と不揮発記憶の動作を完全に分離できる回路構成が必要になる。本研究グループの提案した不揮発性双安定回路は、インバータループ外にトランジスタを介して不揮発性メモリ素子を接続するため、インバータループと不揮発性メモリ素子を電気的に分離できる。したがって、通常のSRAM動作やフリップフロップ動作に影響を与えることなく、不揮発記憶/NVPG動作も実行できる。

[用語2] 強磁性トンネル接合(MTJ) : 薄い絶縁性薄膜(トンネル障壁)を2つの強磁性電極で挟んだトンネル接合構造の二端子素子で、不揮発性メモリMRAMの記憶素子に用いられる。強磁性電極の相対的な磁化状態が平行な場合と、反平行の場合で素子の電気抵抗が異なる。また、100 nm程度以下に微細化されたMTJではスピン注入磁化反転と呼ばれる現象によって、磁場を用いることなく、MTJを流れる電流によって電気的に磁化状態を変化させることができる。

[用語3] 不揮発性パワーゲーティング(NVPG) : マイクロプロセッサやSoCにおけるメモリシステムに不揮発記憶の機能を付加し、高効率に待機時電力の削減を実現するアーキテクチャで、本研究グループから提案された。通常動作と不揮発記憶の動作を分離可能な双安定記憶回路を用いることで、性能劣化をほとんど生じることなくコア内部まで不揮発化をすることが可能となり(ただし、パイプラインなど不揮発化を必要としない記憶回路もある)、従来のパワーゲーティングでは実現できない最適な空間的・時間的粒度のパワーゲーティングを実行できる。したがって、従来技術に比べて、待機時電力の削減効率を高くできる。また、通常動作/不揮発記憶の機能分離によって、マイクロプロセッサやSoCの既存アーキテクチャとの整合性も高い。

[用語4] Break-even time(BET、損益分岐時間) : NVPGでは不揮発記憶を利用するが、これには大きなエネルギー消費を伴う。また、セルの構成によってはリーク電流なども従来の記憶回路に比べて増加していることがある。このような不揮発性記憶回路の導入にともなう余計なエネルギー消費があるため、闇雲に不揮発性記憶回路を用いると、むしろエネルギー消費を増大させてしまうことがある。不揮発記憶回路の導入にともなう余計なエネルギー消費を電源遮断によって埋め合わすことができる最低限必要な電源遮断時間がBreak-even time(BET)である。このBETは損益分岐時間と呼ばれることもある。BETを短くすることで時間的・空間的細粒度のNVPGが実現可能となる。BETの算出にはいくつか方法があるが、最も重要なものは既存の記憶システムと新しく導入した記憶システムとの比較から求めるBETである。新たに導入する記憶回路にどのような回路構成や駆動方式を用いていても、記憶回路であれば必ずBETを算出できる。従来のCMOSロジックシステムにおいてはBETの概念はすでに用いられていたが、本研究グループによって不揮発記憶を用いたシステムに拡張された。

論文情報

掲載誌 : |

ESSDERC-ESSCIRC 2016, Lausanne, Switzerland, September 12-15, 2016. |

論文タイトル : |

Energy performance of nonvolatile power-gating SRAM using SOTB technology |

著者 : |

Y. Shuto, S. Yamamoto, and S. Sugahara |

DOI : |

10.1109/ESSCIRC.2016.7598251 Image may be NSFW. Clik here to view.  |

謝辞

本研究の一部は科学技術振興機構および科研費から支援を受け実施した。VLSIチップは東大VDECおよびルネサスエレクトロニクスの支援によって作製された。

お問い合わせ先

東京工業大学 科学技術創成研究院 未来産業技術研究所

准教授 菅原聡

E-mail : sugahara@isl.titech.ac.jp

Tel / Fax : 045-924-5456

取材申し込み先

東京工業大学 広報センター

E-mail : media@jim.titech.ac.jp

Tel : 03-5734-2975 / Fax : 03-5734-3661