三次元積層メモリーの厚さを1/10に極薄化する技術にめど

―300mmウエハーの厚さ2μm領域でDRAM特性を確認―

要点

- シリコンの厚さを2μm台にするとDRAMの電気特性が劣化

- バンプとTSVを組み合わせた垂直配線に比べ、配線長を1/10に短縮

- テラバイトの高帯域を実現することが可能に

概要

東京工業大学異種機能集積研究センターの大場隆之教授はWOWアライアンス[用語1]と共同で、直径300mmのシリコンウエハーをデバイス層の半分にも満たない2マイクロメートル(μm)級に超薄化することに成功し、この厚さでは半導体メモリー(DRAM)の特性が劣化する現象を初めて明らかにした。

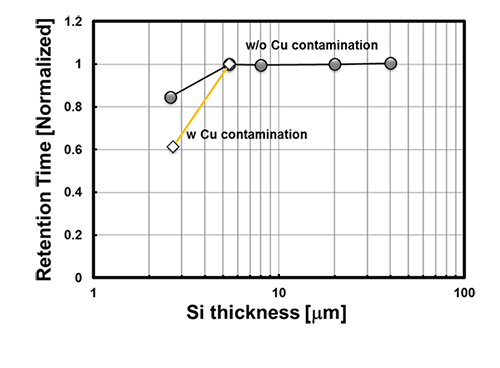

同技術はバンプ[用語2]を用いないWOW積層技術[用語3]に応用することが可能で、ウエハーの薄化は4μmレベルが実用的であることが分かった。ウエハーの厚さが4μmレベルであれば、薄化前と薄化した後のリフレッシュ時間の累積故障率が変わらないことを確認、薄化による新たな原子欠陥が生じないことを実証した。

この薄化プロセスを用いれば、上下積層チップの配線長が従来の1/10以下になり、配線抵抗と配線容量が大幅に低減される。超小型でテラビット(1テラは1兆)級の大規模メモリーへの応用が期待される。

この成果は米国ワシントンDCで12月6~9日に開かれる国際電子デバイス会議「IEDM 2015」で発表された。

背景

半導体メモリーチップを積層し、上下チップを電気接続すれば、積層数に比例したメモリー容量が得られ、極端に微細化しなくても大容量メモリーを得ることができる。上下配線の長さはバンプサイズとチップを貫通する接続孔(TSV[用語4])の長さ(チップの厚さ)で決まり、この配線長を短くすれば配線抵抗と電気容量が低減される。

バンプ接続を前提としたこれまでのTSV配線では、チップ厚さの限界が約50μmであり、バンプとTSVを合わせた長さは約100μmになる。TSV一本当たりのデータ転送速度を少なくし(低周波数)、帯域幅を高めると消費電力が低くなる。このカギを握るのはウエハーの厚さである。だが、どこまで薄くできるのかはこれまで明らかになっていなかった。

研究成果

東工大の大場教授らはウエハーを薄化してから積層し、TSVで直接上下チップを接続配線するバンプレスTSV配線を開発している。この方法を用いれば、バンプが不要になり、薄化プロセスの限界までウエハーを薄くすることができる。FRAM[用語5]、MPU[用語6]、DRAM[用語7]に対して、同研究グループはこれまでに10μm以下の薄化に成功していた。

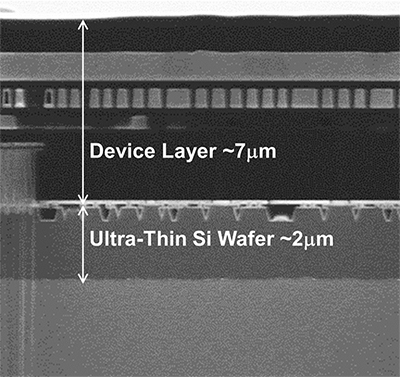

今回はどこまでウエハーを薄くできるかの極限を知るために2μm台の薄化を行った。この厚さはデバイス層の1/3以下の厚さで、機械研削方式では世界で初めての試みである。先端2ギガビットDRAMが形成された300mmウエハーを厚さ775μmから約0.3%の2μmまで薄化した。このような薄化を行うことにより、ようやくデバイス特性の劣化が観察され(観察個所の厚さは2.6μm)、DRAMの限界厚さが4μm前後にあることを明らかにした。厚さ4μmは、DRAMのデバイス層よりも薄く、可視光も透過する。

同薄化技術を利用すると、デバイス層を含めても10μm以下となり、この厚さがTSVの長さになる。これは従来のバンプを利用したTSVに比べ長さが約1/10に短縮される。TSVが短くなると、これに比例して配線抵抗と電気容量がそれぞれ小さくなる。長さが1/10になると配線性能の指標となる配線抵抗と電気容量の積は1/100に減少する。このため4ギガビット、8ギガビット、16ギガビットといったメモリー容量の拡大に合わせてWOWプロセスを使って4層、8層、16層積層しても薄化したチップであれば電気的な課題が解消される。

薄化チップを64層積層しても全体の厚さは800μm以下に収まり、仮に16ギガビットメモリーを積層すれば小型ながら1テラビットの大規模メモリーを実現することができる。このようなメモリーの大容量化を従来の微細化で行っても、ずいぶん先の線幅5ナノメートル(nm)でも達成できない。このように積層されたDRAMは、FOWLP技術[用語8]におけるデバイス部品としても用いることができる。

超薄化でTSVを短く、また小さくできると、加工しやすくなり、生産性が大幅に向上する。同時にバンプの制約がなくなるので、1平方mm当たり1000本から1万本のTSVを形成することができる。

今後の展開

ウエハー厚さ4μmで、このようなTSVを利用すれば低周波数でも高帯域が可能となり、ギガビット転送速度当たりのエネルギー効率が向上する。このためビッグデータ向けのサーバーやスマートフォンをはじめ小型携帯端末の消費電力が大幅に削減される。メニコアMPU[用語9]と組み合わせれば、テラバイトの高帯域を実現することが可能になる。

図1. WOWプロセスを用いて2-μm台まで薄化したDRAMの断面電子顕微鏡写真

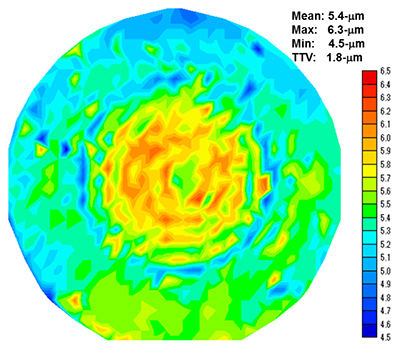

図2. 5.4-μmまで薄化した300mm DRAMのSi厚さ分布

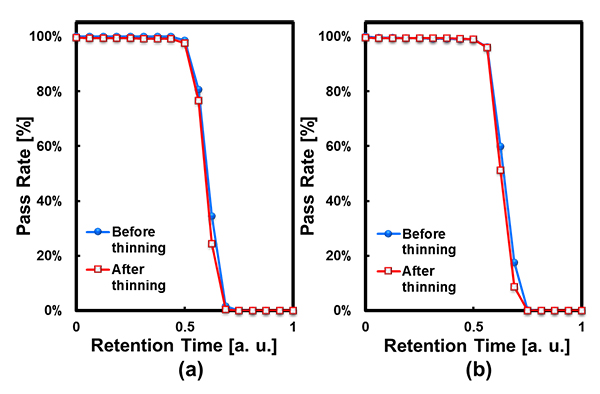

- 図3.

- Si厚さ5-μm台まで薄化したDRAMの歩留まり比較:(a)Cu強制汚染無しと(b)Cu強制汚染有り。Cu強制汚染有り無し関係なく、歩留まりや特性の変化は見られない。

図4. Si残し厚さに対するDRAMのデータ保持時間依存性。4-μm厚さまで薄くしても劣化は見られない。

用語説明

[用語1] WOWアライアンス : 東京工業大学を中心に設計・プロセス・装置・材料半導体関連の複数企業および研究機関からなる研究グループ。薄化したウエハーを簡単に積層することができ、バンプレスTSV配線を用いた三次元化技術を世界で初めて開発した。

[用語2] バンプ : 電極部にメッキで形成した配線接続のための突起。

[用語3] WOW積層技術 : ウエハーの積層(Wafer-on-Wafer)で大規模集積回路を作製する三次元集積技術。積層方法には、チップ同士の積層(Chip-on-Chip)、チップとウエハーの積層(Chip-on-Wafer)があり、COC、COW、WOWの順に生産性が高くなる。

[用語4] TSV : Through-Silicon-Viaの略で、シリコンウエハーを貫通させ埋め込み配線で上下チップチップを接続させる接続孔。最近では、シリコン材料以外にも配線するため、前工程における垂直配線(vertical interconnects)とした方がわかりやすい。

[用語5] FRAM : Ferroelectric RAMの略。強誘電体を利用した不揮発メモリーの一種。

[用語6] MPU : Micro-Processing Unitの略。コンピューター内で基本的な演算処理を行う超小型演算装置でコンピューターの心臓部に当たる半導体チップ。

[用語7] DRAM : Dynamic Random Access Memoryの略。コンピューターに利用される揮発メモリーの一種。

[用語8] FOWLP : Fan-out Wafer Level Packageの略。再配線されたウエハーにデバイスチップを搭載し、チップとウエハーを配線接続するものである。バンプを用いない分薄くなり、小型パッケージが可能になる。

[用語9] メニコアMPU : 複数の論理回路(コアプロセッサ)を有するMPU。2個あればデュアルコアプロセッサと呼び、通常2桁以上のコアプロセッサを有するMPUに対して用いられる。

学会発表

学会名 : |

2015 IEEE International Electron Devices Meeting (IEDM) |

発表タイトル : |

A Robust Wafer Thinning down to 2.6-μm for Bumpless Interconnects and DRAM WOW Applications |

発表者 : |

Y.S. Kim, S. Kodama, Y. Mizushima, T. Nakamura, N. Maeda, K. Fujimoto, A. Kawai, K. Arai and T. Ohba

|

問い合わせ先

東京工業大学異種機能集積研究センター

秘書 沼澤文恵

Email : numazawa.f.aa@m.titech.ac.jp

Tel : 045-924-5866

取材申し込み先

東京工業大学 広報センター

Email : media@jim.titech.ac.jp

Tel : 03-5734-2975 / Fax : 03-5734-3661